What is Neotron?

Neotron is an attempt to make computers simple again, whilst also taking advantage of the very latest in programming language development. We are saddened by chat clients that require multi-Gigabyte installs, and systems with hundreds of millions of lines of source code that no one person could ever hope to understand. We want to build a machine that is sized for an individual to comprehend, not a trillion-dollar corporation.

If you want a pithy sound-bite, it's like CP/M for tiny ARM microcontrollers, but written in Rust.

Tell me more...

Neotron is based around four fundamental components.

- A standardised OS interface, for portable Applications to call. This provides APIs for reading/writing files, accessing devices, writing to the screen, playing audio, etc.

- A standardised BIOS interface, for the Operating System to call. The BIOS abstracts the specific hardware implementation of the Video, Audio, UART, SPI, I2C, GPIO, Disk Drive, Parallel Printer, Keyboard and Mouse interfaces. By using the BIOS, we should be able to run the exact same Neotron OS on a variety of different microcontrollers.

- Use of the Rust Programming Language to write as much of the software as possible (we avoid raw assembler as much as possible, but we're happy to port existing applications that are written in C even if we avoid that language in the system software).

- The ARM Thumb-v7M instruction set (as supported by ARM Cortex-M based microcontrollers from the M3 and up). This is what allow us to run the same programs on microcontrollers from different vendors.

Looking back at classic home computers of the 1980s and early 1990s though, we see systems that were (and still are) simple enough to understand, or even - with time - to learn to master. Here's a rough comparison with just a few of the classic systems we have taken as inspiration (where not otherwise specified, these are the first version launched of a given system):

| Feature | Neotron 32 | Neotron Pico | IBM PC | BBC Micro | Commodore 64 | Apple Macintosh | Amstrad PCW | Amiga | Acorn Archimedes |

|---|---|---|---|---|---|---|---|---|---|

| Launch Year | 2020 | 2021 | 1981 | 1981 | 1982 | 1984 | 1985 | 1985 | 1987 |

| Instruction Set | ARMv7E-M | ARMv6-M | Intel x86 | MOS 6502 | MOS 6502 | Motorola 68k | Zilog Z80 | Motorola 68k | ARM v2 |

| CPU | Cortex-M4 | 2x Cortex-M0+ | 8088 | 6502A | 6510 | 68000 | Z80A | 68000 | ARM2 |

| Clock Speed | 80 MHz | 2x 133 MHz | 4.77 MHz | 2 MHz | 1 MHz | 8 MHz | 4 MHz | 8 MHz | 8 MHz |

| Low Level OS | Neotron BIOS | Neotron BIOS | IBM BIOS | Acorn MOS | KERNAL | Toolbox | XBIOS | Kickstart | RISC OS |

| High Level OS | Neotron OS | Neotron OS | PC-DOS 1.0 | Acorn MOS | N/A | System | CP/M Plus | AmigaDOS | RISC OS |

| Shell | Neotron Shell | Neotron Shell | COMMAND .COM | BBC BASIC | BASIC v2 | Finder | CP/M CCP | Workbench | RISC OS Desktop |

| Primary Language | Rust | Rust | Assembly / C | Assembly | Assembly | Object Pascal | Assembly | BCPL / C | Assembly / BBC BASIC |

| ROM | 256K | 2048K | 8K | 32K | 16K | 64K | 256 bytes | 256K | 512K |

| RAM | 32K | 256K | 16K to 256K | 32K | 64K | 128K | 64K | 256K | 512K |

| Self-hosting | No | No | Yes | Yes | No | Yes | Yes | Yes | Yes |

The IBM PC BIOS was stored in a ROM chip on the motherboard. It provided a certain level of hardware abstraction, with APIs for writing to the screen, setting the video mode and reading/writing from block devices such as floppy drives. The BIOS initialised the hardware, loaded the first sector of a chosen block device into RAM and then executed the code contained within. This was the Boot Sector and contained enough code to load the rest of the Operating System. PC-DOS made use of BIOS APIs, but often games would bypass both MS-DOS and the BIOS and access hardware directly. Famously, Microsoft was able to sell copies of PC-DOS (relabelled as MS-DOS) to manufacturers of 'PC compatibles', provided they had a BIOS ROM which offered the same (reverse-engineered) API as the IBM BIOS.

The BBC Micro had a very advanced Operating System for the time, known as the Acorn Machine Operating System (MOS). You could add extra ROMs to the system, such as the Disk Filing System (DFS). BBC BASIC was also very advanced for the time, including a built-in 6502 assembler.

The Commodore 64 contained two 8 KiB ROM chips - one contained the OS (called the KERNAL) and one contained a rebadged Microsoft 6502 BASIC. The KERNAL was very low level and Microsoft BASIC didn't include any commands to produce graphics or sound - developers were expected to interact with memory mapped hardware directly. The C64 KERNAL could be assembled using PET RESIDENT ASSEMBLER on a Commodore PET, but the Microsoft BASIC source code was written on a PDP-10 using the MACRO-10 assembler.

The original Apple Macintosh had a ROM on the motherboard which initialised the hardware and drew a graphical image on the screen indicating that the user should insert the System disk. The ROM then loaded the OS (known as System up to version 7, and Mac OS for versions 8 and 9) into RAM, along with a graphical desktop called Finder. Applications on the Macintosh (including the Finder) made use of a number of graphical routines stored in the ROM, known as the Macintosh Toolbox.

The Amstrad PCW8256 was similar to the Amiga 1000 in that the main BIOS was loaded from floppy disk. Going further than the Amiga though, the PCW didn't include a ROM chip at all. Instead the 256 bytes of bootstrap code were loaded from the microcontroller responsible for managing the printer interface. The bootstrap loaded the so-called XBIOS from floppy disk into RAM. XBIOS then initialised the hardware and loaded CP/M Plus (also known as CP/M 3.0). The shell was the familiar CP/M Command Console Processor (CCP), and both the OS and the CCP were the same across a wide range of CP/M machines from many different vendors, with the BIOS providing the hardware abstraction layer.

The Amiga 1000 hardware didn't include much in the way of a ROM at all. A basic bootstrap program stored in ROM was able to load most of the low-level OS (known as Kickstart) into a special write-only area of RAM. Kickstart could then load either the particular game being played, or AmigaDOS and a graphical shell known as Workbench. On later machines (such as the A500), the Kickstart was stored in ROM.

The Acorn Archimedes was first shipped with an OS in ROM called Arthur, but this was soon replaced with the more familiar RISC OS 2 (and later RISC OS 3). The entire OS - bootstrap, HAL, filesystem and GUI - was one on ROM chip, meaning it booted up very quickly, without needing to read from any sort of disc.

The key feature for many these systems (apart from the Commodore 64), was portability across other machines in the family (or, indeed, third-party clones). The PC, the Amiga, the Macintosh and CP/M all provided a platform, and if you respected certain limits when writing your software, that software was then portable across all the systems which provided that platform. For Neotron, this is a key concept - because microcontrollers vary so wildly, we have a BIOS that implements hardware abstraction, just like with the PC or CP/M machines. We then run a standard OS (indeed, the same OS image should work on every Neotron machine - more-or-less), either from ROM or loaded into RAM by the BIOS. On top of the OS is the text-mode Neotron Shell (like CP/M's CCP, or MS-DOS's COMMAND.COM). Booting to a graphical desktop would be nice, but given the Neotron 32 only has 32 KiB of RAM (barely enough for a low resolution frame-buffer), text mode is the default. Ultimately, a Neotron 32 should be able to 'compete' on a functional level with an un-expanded IBM PC 5150 or a BBC Microcomputer Model-B. The Neotron Pico meanwhile, could be more like a Macintosh, Archimedes or Amiga in terms of functionality and in time we do hope to develop a GUI for this system.

As with the CP/M and MS-DOS machines, we hope that in the future there will be a wide range of machines in the Neotron family. These Neotron systems won't generally aim to be super cheap, although we will tend to target commodity microcontrollers that only cost circa $10 or less, so they shouldn't be outrageously expensive. They will, however, aim to be usable computers that can do interesting things, while being simple enough to understand in their entirety and open enough to allow you to gain that understanding.

What can I do with it?

You can do what you can do with most 1980s home computers:

- Type things on the keyboard.

- Use a joystick or a mouse.

- Manage files on internal or removable storage.

- Load programs from internal or removable storage.

- Type in your own programs.

- Put text and graphics on the screen.

- Make various beepy noises.

- Connect various internal expansion cards or external peripherals.

- Expand the system in ways the designer couldn't imagine.

But most importantly, you can learn the fundamentals of what it takes for a computer to be a computer. And you can study the source code and hardware schematics required to make that happen. You can even take the designs and go off and produce your own version - maybe to add a specific interface for a particular peripheral that interests you - all with no licence fees to pay.

What can't I do with it?

A Neotron system will probably never:

- Support multiple processes (although Windows 3.1-style co-operative task switching is plausible).

- Support 3D graphics (e.g. OpenGL).

- Support virtual addressing (i.e. make use of an MMU).

- Be POSIX compatible.

- Have a huge software library (or probably any real library of software).

- Run existing MS-DOS, Windows or Linux programs.

- Be able to run

rustc. - Have a port of Rust's

libstd. - Be directly targetable from Rust with

--target=thumbv7em-unknown-neotron-eabi. - Be useful for day to day use.

- Be finished.

If you want a decent open-source UNIX Operating System, have a look at FreeBSD (or NetBSD, or OpenBSD). If you want a small teaching-oriented open-source UNIX Operating System, look at XV6, or maybe MINIX 3. If you want to learn about Linux, try Linux from Scratch. If you want to learn an ancient Arm based Operating System which still has a flavour of the original BBC Microcomputer, look at RISC OS (it's open source now). If you want a proper OS written in Rust, look at Redox. And if you want to do any of that on a system you don't have, try qemu, or rpcemu.

Is this a good idea?

It's certainly not a profitable idea. It's not even likely to be an efficient use of our time and resources. But it is proving to be a fun and educational project to work on, and we hope others find it useful and/or enjoyable too.

But what about ${EXISTING_PRODUCT}?

Raspberry Pi

Yes, you can buy a Raspberry Pi for a little as $5 - and it's a wonderful product that has done arguably more than anything since the BBC Microcomputer in terms of putting hardware you can actually program into the hands of young people. But, the downside is that you get a big, complicated piece of silicon, a proprietary GPU subsystem, 25 million lines of kernel source code, and even more in a user-land which has parts dating back over 30 years. No one person could hope to understand all of that! While we could probably port the Neotron OS to the Raspberry Pi, we'd have to treat the video sub-system as a black-box (like RISC OS does) and the complexity and lack of documentation of that subsystem presents a big barrier to fully understanding the system. Not to mention the the fact that only partial schematics are available, there are no PCB designs available, and there's no general availability on the main processor. It does what it needs to do for its target market quite admirably - but it's not a Neotron.

x86 based systems, like the original IBM PC

You could build yourself a clone of the original IBM PC (kits do exist), but it involves a lot of components that are very difficult to obtain nearly 40 years since that design first came out. Rust is also designed around a flat memory model (rather than the segmentation:offset model used by the 16-bit 8086), and that means using at least a 32-bit Intel 80386. And, of course, these are plain CPUs rather than microcontrollers, so you'll need to find a 'chipset' containing interrupt controller, DRAM memory controller and timers; as well as separate video, sound and IO sub-systems. Our System-on-Chip based design simplifies the motherboard design and reduces cost, and unlike with modern x86 SoCs, we don't have to deal with complicated legacy subsystems such as UEFI, ACPI or PCI.

6502 based systems (like the PE6502 and Commander X16)

You could build a 6502 based system, and many people do, but the Rust programming language doesn't (and probably never will) support an 8-bit CPU with only 256 bytes of stack.

68000 based systems

At the present time, there is no 68k backend in LLVM. If there was, a 68000 system would certainly make an interesting alternative to Neotron, although the 68000 processors available are more expensive and less powerful than a modern commodity Arm microcontroller.

PowerPC based systems

LLVM does have a PowerPC backend, but unfortunately most PowerPC based chips only come in monster 380+ pin BGA packages, with multiple power rails. This unfortunately puts them beyond the scope of a simple hobby project, much as the author would love to build a machine that harks back to the IBM RS/6000 and Power Macintosh machines of the 1990s.

RISC-V based systems

There are an increasing number of RISC-V based microcontrollers with very small SRAMs, matched by an increasing number of multi-core 64-bit SoCs designed to run Linux from a huge bank of DDR3. At the current time, however, there isn't much in the middle.

A Neotron system built around an open-source RISC-V code run from an FPGA would be an interesting way to increase the openness of the system and remains a future possibility. The simplicity of the RISC-V ISA is also appealing, as compared to the, umm, evolved nature of ARMv6-M.

SPARC based systems

The Gaisler LEON3 is available in VHDL form under the GPL, along with a number of other components required to make a full SoC. The LEON3 implements the SPARC V8 ISA, support for which is available in the Rust compiler. However, this would require an FPGA based system and it's unknown whether the full GRLIB SoC would fit into any of the FPGAs supported by the various open-source FPGA synthesis tools (such as the Lattice iCE40).

Atmel AVR based systems

Many people have built Atmel AVR based systems, but those CPUs are fairly limited in terms of performance and tend to need to be programmed in raw assembler, or at least non-portable C (such as when storing strings in program memory with a 24-bit pointer instead of in data memory with an 8-bit pointer). There is a Rust AVR port, but it's only in an alpha state at the moment.

MIPS32 based systems, like the PIC32

The PIC32 family would make a very interesting home computer. Indeed, a PIC32 can be found in the Colour Maximite. I think it is telling though that the next revision of the Colour Maximite switched over to a Cortex-M7 based STM32H7. You could also point to the fact that MIPS themselves have publicly switched to producing RISC-V designs that maybe this architecture doesn't have the best future ahead of it.

What is this book?

This book describes the Neotron system - from the hardware schematics, all the way up to how to write applications for the system. It is intended to be the canonical reference, although where the source code differs from what is described in this book, we reserve the right to be pragmatic and change either to match the other (or leave them in disagreement...). This book also represents our latest thoughts on a particular topic, and the source code may lag behind while we get around to the implementation. We endeavour to note where this is the case.

Versioning

Each component has a semantic version number - major.minor.patch. The association is:

- The BIOS will require a compatible hardware version.

- The OS will require a compatible BIOS version.

- The Shell and Applications will require a compatible OS version.

Licence

Neotron is designed to be open - the user must have free rein to inspect the source code and the schematics, and change them to suit their needs. To this end, the main BIOS and OS implementations are licensed under the GNU Public Licence v3 or any later version. To encourage the adoption of Rust for embedded development, most of the library crates developed for this project are licensed under both the MIT and Apache 2.0 licences, just like the Rust compiler itself. We do intend to sell a range of kits and pre-built PCBs, but you can (and should!) take our designs as inspiration and put your own spin on them.

This book is licensed under Creative Commons CC-BY-SA 4.0. Any source examples in this book may also be used under the MIT or Apache 2.0 licences.

Credits

Neotron started as a project called 'Monotron', by @thejpster. This was based on the work of the Rust Embedded Working Group, and inspiration from the following (in no particular order):

- Colour Maximite - A modern PIC32 based single-board home computer.

- PE6502 - A modern 6502 based single-board home computer.

- Gigatron - A single-board home computer, with a custom CPU built from TTL logic chips.

- Commander X16 - A single-board home computer, with a 6502 and an FPGA based video chip.

- Craft - Demonstrates bit-bashing VGA from an AtMega88

- AVR-ISA - Demonstrates driving an ISA bus (and an ISA VGA card) driven from an AtMega128

- The Commodore 64C - @thejpster's first home computer

- The BBC Microcomputer range (the Model B through to the Archimedes A3000) - as used in UK schools in the 1980s

- The Amstrad range of CP/M machines, particularly the PCW9512

After meeting @IGBC at Oxidize 2019, discussions started around a next-generation system with higher performance. This led to the Neotron 1000, and then to the whole Neotron concept. We've also great benefited from conversations with @jamesmunns, and others in the Rust Embedded Working Group.

Introduction

The software in a Neotron system is divided into layers. This approach allows each layer to concentrate on its own areas of responsibility (known as separation of concerns). These layers are arranged into a stack, with the interface to the physical hardware at the bottom, and the user application at the very top.

+---------+-------------+

| | |

| Shell | Application |

| | |

+---------+-------------+

| |

| Operating System |

| |

+-----------------------+

| |

| BIOS |

| |

+-----------------------+

| |

| Embedded HAL |

| |

+-----------------------+

| |

|Peripheral Access Crate|

| |

+-----------------------+

| |

| Raw Hardware |

| |

+-----------------------+

The Neotron BIOS

Introduction

The Neotron BIOS is the hardware-abstraction layer for the Neotron Operating System. It allows the OS to run on different hardware platforms with the minimum number of changes.

+-------+-------------+

| | |

| Shell | Application |

| | |

+-------+-------------+

| |

| Operating System |

| |

++===================++

|| ||

|| BIOS ||

|| ||

++===================++

| |

| Raw Hardware |

| |

+---------------------+

What goes in the BIOS and what goes in the OS?

As a general rule, the BIOS should contain all the drivers for the main system-on-chip (SoC) in that particular Neotron system. It should also understand which pins on the SoC have been assigned to which functions. It is therefore a function of the netlist for the main PCB, and the components fitted to it.

If a particular function might apply to SoCs from different manufacturers, or to an expansion card that could be inserted into multiple different models of Neotron system, it is probably better placed in the Neotron OS.

Interfaces

A BIOS should offer an interface upwards to the OS so that the OS can:

- Discover the hardware in the system

- Select and use various video modes:

- Text modes

- Bitmap graphics modes

- Split modes

- Layered Modes

- Hooking video scan-line interrupts

- Read any keyboard key events

- Access (read from, write to and/or configure) any Serial/UART interfaces

- Access any I²C buses, and any devices attached to its bus

- Access any SPI buses, and any devices attached to its chip selects

- Access any USB Host Controllers, and any USB devices attached

- Access any block devices, via whatever interface they are connected to

- Read from / write from any audio FIFOs

- Configure a periodic 'system tick' timer

- Obtain / set the current calendar time

- Measure elapsed time since boot-up (e.g. in microseconds)

- Hook interrupts for the external IRQ lines

- Access any OS-specific non-volatile configuration

On top of these APIs sits the Neotron OS, which should be portable with almost zero changes to any device with a Neotron BIOS. While you could write an application which uses the BIOS directly, most applications will use the higher-level APIs exposed by the Neotron OS.

Configuration

Many Neotron sytems will have an element of user configuration to them - e.g. which cards are fitted to which expansion slots, or whether an optional item has been fitted to the PCB. To handle this, it is expected that the BIOS have some kind of configuration application, and some non-volatile storage that will hold the configuration across a power cycle. Typically this will be in the battery-backed real-time clock, but it could equally be in an EEPROM.

Calling a BIOS API

On ARM systems, calling a kernel API is usually done through a SWI or SVC

machine instruction. This effectively triggers an interrupt, putting the CPU

into interrupt mode where it starts executing the SWI exception handler.

Unfortunately, calling the SWI instruction and passing arguments via registers

can only be performed from assembly language, and is not supported by the

cortex-m crate at this time.

Monotron instead used a simple alternative - when the application was started by

the OS, the OS passed it a pointer to a structure of function pointers. You can

think of this as being like an old-fashioned jump table. When the application

wanted to get the OS to do something, the application just called the

appropriate function through the given pointer. The downside was that the

Monotron OS functions used the same stack as the application, and it was

impossible for an application to exit back to the OS unless it returned from

main (i.e. there was no exit() function you could call). The Neotron BIOS

accepts these downsides in the same of simplicity, and takes the Monotron

approach - at least for the BIOS-OS ABI.

The BIOS is responsible for starting the system and performing hardware

initialisation. It will also search for the OS, either in Flash memory, on disk, or

perhaps even loaded over a UART. The OS then has its initialisation function

called, to which the structure of BIOS function calls is passed. The

initialisation function is specified as a function pointer stored at a

specific offset (most likely the first four bytes of the OS image). To avoid

undefined behaviour, that initialisation function should memset the .bss

section to all-zeroes and, if necessary, initialise the .data section using

values stored in Flash memory.

Most of the BIOS APIs will be 'blocking' - that is, the function call will not return until the BIOS has completed the operation (e.g. read the sector from disk, or written the bytes to the UART). It is possible in the future that BIOS APIs will be added which allows operations to be asynchronous - that is, to return immediately once the operation has been queued and then either call some function or set some marker value in memory once the operation has been completed. Such an API is more complex to develop, and has interesting challenges around ensuring the memory passed to the function remains available (i.e. it isn't just on the stack of the calling function). However, these APIs are generally more efficient in terms of CPU time, as the CPU does not have to waste cycles spinning in the main thread whilst it waits for the operation to complete - for example, you could be writing some sectors to disk and performing an I²C read from the HID controller asynchronously, whilst also calculating new display graphics and audio in the main thread.

For now however, the blocking APIs were sufficient for MS-DOS, and they will be sufficient here.

Why split the OS and the BIOS?

We could take the Linux / Windows NT approach, with a boot-loader that performs the bare minimum required to get the kernel (or, in our case, what we call the 'OS') into RAM and start it running. The boot-loader for a PC is usually a UEFI BIOS but on an older system might be an IBM PC-compatible 'legacy' BIOS. The operations performed typically include DRAM setup, rudimentary console setup (either frame-buffer or over UART) and accessing the kernel from some kind of block device or non-volatile memory (e.g. SD Card). The kernel then replaces the boot-loader, which is never used again.

Because our Neotron systems generally have Flash memory, we don't actually need a boot-loader in that sense. Instead, we implement something more like the interface provided by an IBM PC-compatible 'legacy' BIOS for running MS-DOS, which itself was modeled on the design of CP/M's BIOS and BDOS components. In that case, the BIOS provides a fixed application binary interface (ABI) which is unchanging. This allowed development of MS-DOS (and CP/M) to be performed against a fixed target (or rather, multiple implementations of a fixed ABI), allowing the same copy of MS-DOS or CP/M to run on a variety of PCs from a variety of manufacturers. The alternative would be to require all of the drivers and board support packages to be added into OS kernel (as usually happens with Linux), or for the drivers to be loaded from disk at boot-up (as with Windows). We have seen with Linux that, for whatever reason, not all boards and peripherals get their driver support upstreamed, and because Linux does not maintain a binary ABI for drivers, anything that isn't upstream quickly becomes obsolete. As a case in point, try to update the version of Linux used on circa-2015 Android tablet - you'll quickly find yourself stuck on an old Kernel version with bespoke patches (or worse, binary blobs) that weren't upstreamed or open-sourced. Whilst Windows maintains a binary ABI for drivers, they are usually closed-source and of varying quality, leading to system instabilities that are almost impossible to debug.

The Neotron approach allows for:

- Less centralised development: the Neotron developers do not need to look after (or even know about) your BIOS implementation, as long as it meets the ABI

- Easier upgrades: any system with a Neotron BIOS should be updateable to a newer version of the Neotron OS

- A smaller OS: the amount of code in the OS (e.g. for drivers) is reduced, which means the OS is easier to understand and review

- Simpler builds: everyone can run basically the same build of the OS (subject to some constraints about the specific Arm architecture being targeted) as everything board specific is in the BIOS

- Better portability: because anything CPU specific is in the BIOS, it should

- in theory - be possible to port the Neotron OS to another CPU architecture with just a re-compile.

The downsides are:

- It's slower: there can be no optimisation across the OS / BIOS boundary.

- Limited support: it's harder to add new classes of peripheral bus (e.g. if we ever wanted to add support for I3C), as the old BIOSes won't know about them.

- Harder to design: a binary-stable ABI is harder to design in Rust than a

plain function-call API, as you have to use

extern "C"and#[repr(C)], and therefore can't use significant portions of the Core Library in your API definition.

Testing

For BIOS testing, there will be a special 'cut-down' version of the OS which offers only a very basic console, and direct access to all the BIOS APIs via that console.

Character Sets

The video display engines on a Neotron system only support monospaced 8-bit fonts (that is, fonts with only 256 glyphs and where each glyph occupies the same horizontal space on screen), and so the mapped text buffer memory works exclusively in the character set defined by the font. The rest of the BIOS API works exclusively in UTF-8 encoded text, and mapping functions are provided by the BIOS to convert from a Unicode codepoint to the font-specific character set. Generally the first 128 glyphs will match basic ASCII (and hence the first 128 Unicode code points) for performance reasons, although that isn't necessarily required.

It is possible that Neotron could be adapted to support multi-byte character sets (e.g. for Chinese, Japanese or Korean text display where more than 256 glyphs are required), but there is no support for that planned at this time.

The Neotron BIOS - API Calls

The BIOS exports its functionality to the OS through a structure of function pointers. This structure exists in BIOS memory (probably in Flash, but it could be in RAM) and a pointer to it is passed to the Operating System (OS) when the OS is started by the BIOS.

The OS should only access the hardware through the function pointers contained within the given structure. The only assumption the OS can make is about the location of the memory regions defined in its Linker Script.

The BIOS API is documented at https://docs.rs/neotron-common-bios/latest/neotron_common_bios/.

The Neotron OS

The Neotron OS is the hardware-agnosting implementation of the Neotron API. It uses the BIOS to interact with the hardware, allowing it to run on different hardware platforms with the minimum number of changes.

+-------+-------------+

| | |

| Shell | Application |

| | |

+=======+=============+

| |

| Operating System |

| |

+=====================+

| |

| BIOS |

| |

+---------------------+

| |

| Raw Hardware |

| |

+---------------------+

It should implement:

- File/Device handling (open, read, write, seek, etc)

- A FAT16/32 compatible filesystem with MS-DOS MBR partitions (max 2 TiB disk size - 232 sectors of 512 bytes)

- A text-mode console, with cursor

- Basic line-based input and character based raw input

- Simple bitmap graphics primitives (lines, rectangles, fill, etc)

- An audio synthesiser

- Input/output stream handling

- Digital (Atari) joystick support

- A TCP/IP networking stack

- MIDI support

- Jumping to applications located in RAM or ROM, giving them access to the OS

- Supporting special 'shell' applications which can chain-load small programs (e.g. command-line utilities) without being unloaded

- Memory allocation/deallocation routines

- Run-time volume mounting/unmounting

Selected non-goals (i.e. things we aren't going to support) include:

- Co-operative multi-tasking

- Pre-emptive multi-threading

- Virtual Memory (although we might support a special API for paging to and from disk)

- Processes / process isolation

Our ultimate goal is that one day we could offer a version of the Rust Standard Library (std) which uses the Neotron OS API - albeit without the sub-process and thread support.

Programming on the Neotron usually involves first loading the specific interpreter for that language - unless you've swapped out the standard shell for something like a BASIC interpreter.

Filename Convention

Files live in volumes. Volumes on fixed or removable disks must be formatted with the FAT12, FAT16 or FAT32 filesystem and live either live in a disk partition identified by a PC Master Boot Record (with a suitable Filesystem Type), or live at the start of the drive. Volumes are allocated a volume number, starting with 0:, then 1: etc. File paths are relative to a volume number. Paths are separated with a / character. The root directory is called /.

When a volume has a name, you can refer to it as <name>: instead of <id>:. For example work:/Documents/hello.txt refers to a file called hello.txt inside a folder called Documents which lives on a volume called work.

It is an error to try and create a file containing a : character. Any files or directories which do contain invalid characters are as if the character was replaced with _. When a directory contains multiple files with the same name, any attempt to read the file will only be able to access the one that is found first. Any attempt to create a new file will cause any existing files of the same name in the same folder to be deleted.

For example:

0:/> dir 1:

Listing files in 1:/

FOO.TXT 1234 2019-10-17 23:20:01 A--

COMMANDS.SH 34 2019-10-17 23:20:11 AR-

FOLDER <DIR> 2019-09-13 20:20:11 D--

0:/> dir 1:/FOLDER

Listing files in 1:/FOLDER

BAR.TXT 1234 2019-10-18 10:11:13 ---

0:/> cd 1:/FOLDER

1:/FOLDER> dir

Listing files in 1:/FOLDER

BAR.TXT 1234 2019-10-18 10:11:13 ---

1:/>

Unlike MS-DOS, which has a separate current directory for each volume (i.e. drive letter), Neotron maintains a UNIX-like single current directory which includes the name of the current volume. Where a volume is given without a directory path, the root directory (/) is presumed.

File Permissions

Files can be opened as read-only (write-none), write-truncate or write-append. Because Neotron is single-tasking and non-re-entrant, there is no support for lock files or exclusive file creation, but files are locked when they are opened so they can only be opened once at any one time. Files on disk support the standard FAT16/FAT32 attributes - Archive, Read-Only, Hidden and System. Seeking uses 64-bit byte offsets, although note that FAT32 limits files to 4 GiB in size.

File Operations

A file handle, whether pointing to a file on a volume, or to a Special Device, generally has the following functions available. These functions broadly follow the POSIX model.

-

read- obtain some bytes from this handle. A&mut [u8]is supplied, and either an integer is returned which reports how many bytes in that buffer were filled by the function call, or an error is returned. The call will wait until the buffer is full, or the timeout has been met - the timeout may be zero, some finite value, or infinite. Some files (e.g. block devices) only support reading fixed size blocks and attempts to read any other size block will give an error. -

write- sent some bytes to this handle. A&[u8]is supplied, and either an integer is returned which reports how many bytes from that buffer were sent by the function call, or an error is returned. The call will wait until all the bytes have been sent, or the timeout has been met - the timeout may be zero, some finite value, or infinite. Some files (e.g. block devices) only support writing fixed size blocks and attempts to write any other size block will give an error. -

seek- adjust the current pointer in the file. Files opened for reading start with the pointer at the beginning. Files opened for writing start with the pointer at the end. Some special devices are not seekable and this function will return an error. The pointer can be adjusted with a number of bytes relative to a) the current position, b) the start of the file, or c) the end of the file. Seeking beyond the end of a file on disk is not supported. Some files (e.g. block devices) only support seeking to particular offsets (e.g. a multiple of the block size) and attempting to seek to any other offset will give an error.

Special Devices

There are special devices which look like files, but are not. They have names which are like volumes, but contain a '$' character. It is an error to try and use a regular volume with $ in the name. Where the device name contains an x, the x should be replaced with a single digit (e.g. 0 or 1) to identify a specific device.

CON$:- The console. You can read from here to get line-buffered text input and write here to put UTF-8 text on the screen (with ANSI code sequence support).KBD$:- The raw keyboard. You can read from here to get raw keyboard events (such as Up Arrow key, or Page Down).TIME$:- Gets/sets the system time (read/write).GFX$:- A bitmap framebuffer device.PRNx$:- A printer. Write here to send data to the printer, read to get print status.DISCx$:- An SD card or other block device (can read/write raw 512 byte blocks).SERx$:- An RS-232 serial device (read/write).TONEx$:- A tone generator device (write-only).PCMx$:- A PCM device (write for playback, read for record).JSx$:- A Joystick (read-only).

Additional parameters may be specified after the $, separated by ;. For example:

SER0$bps=9600;parity=N;timeout=100:- The first RS-232 serial device, at 9600 bps, with a 100 frame read/write timeout.PCM0$channels=2;bit=8;samplerate=8000:- A PCM interface configured for stereo 8kHz 8-bit.

Special devices do not support filenames or paths. To access something like a network volume, the volume must be mounted and given a normal volume ID. The API for this is TBD.

Writing to CON$:

The Console device CON$:, like every other file, is a bi-direction octet pipe. Unfortunately, one octet is not enough to represent the full set of characters a modern computer needs to support. Rust handles this by insisting that text (&str string slices and String owned strings) is in Unicode Translation Format 8 (UTF-8). This is a mechanism by which Unicode characters (which are around 21 bits in size) can be encoded as between one and six octets. The useful property is that the first 127 Unicode characters map to a single octet, which makes it interchangeable with standard ASCII.

In text mode, most Neotron systems will only have one octet avilable per text cell to record which particular character being displayed in that cell, therefore placing a limit of 256 different glyphs in any given font. The font must therefore also provide a translation function which can convert from a 21-bit Unicode character to an octet for storage in the screen buffer. Typically the fonts will follow some standard 8-bit code page, such as Code Page 850, but this is not enforced and aside from some characters failing to render correctly on the screen, is invisible from an application point of view.

Ordinarily the OS will maintain a cursor position and any text written to the Console will be added to the screen at that position. The screen has a nominal width and height, and when the cursor gets to the end of a line it moves down to the start of the next line. The console will also handle the following special characters in the usual way:

| ASCII Code | C Escape Sequence | Keypress | Name | Function |

|---|---|---|---|---|

| 0x07 | \a | Ctrl+H | Bell | Produces a beep from the speaker |

| 0x08 | \b | Ctrl+H | Backspace | Move to one character to the left |

| 0x09 | \t | Ctrl+I | Tab | Move to next column which is a multiple of 8 |

| 0x0A | \n | Ctrl+J | Line Feed | Move to start of next line |

| 0x0C | \f | Ctrl+L | Form Feed | Clear the screen and move to start of first line |

| 0x0D | \r | Ctrl+M | Carriage Return | Move to start of current line |

For some text mode applications, more precise control is required over the position of the cursor, the colour of the text, and so on. This is acheived by inserting ANSI Escape Sequences into the octet stream. The sequences supported are a subset of those defined in ECMA-48, and broadly align with those commonly used on Linux/UNIX systems, although support for the specific colours, etc, depends on the video support available in the BIOS. In the following table:

ESCmeans Escape. It is represented by the single Unicode characterU+001B(0x1Bin UTF-8).CSImeans Control Sequence Introducer. It is represented by the the single Unicode characterU+009B(or0xC2 0x9Bin UTF-8), or alternatively the two character sequenceESC [(0x1B 0x5Bin UTF-8).- The lowercase characters n and m represent optional integer parameters, rendered as decimal in ASCII using the characters

0to9. - Rows and Columns are 1 indexed, with

1,1being the top left of the screen.

| Sequence | Function |

|---|---|

| ESC c | Reset to Intial State |

| CSI n A | Cursor Up n (default 1) rows |

| CSI n B | Cursor Down n (default 1) rows |

| CSI n C | Cursor Forward n (default 1) columns |

| CSI n D | Cursor Back n (default 1) columns |

| CSI n ; m H | Cursor Position to row n (default 1) and column m (default 1) |

| CSI n [ ; m ] m | Select Graphic Rendition (see below for valid parameters) |

The Select Graphic Rendition codes are as follows. Note that multiple codes can be specified in one escape sequence, separated by semicolons. Most of the codes only affect text which is subsequently printed to the console - the only exception is the font select commands 10 to 13 which change the font for the entire screen. The loading of custom fonts is performed through a separate OS call.

| SGR Code | Function |

|---|---|

| 0 | All attributes off |

| 1 | Subsequent text is bold |

| 8 | Subsequent text is concealed (replaced with *) |

| 4 | Subsequent text is underlined |

| 7 | Swap foreground/background colours |

| 10 | Select default font (usually VGA Code Page 850) |

| 11 | Select alternative font 1 (usually Teletext) |

| 12 | Select alternative font 2 (user defined) |

| 13 | Select alternative font 3 (user defined) |

| 28 | Turns off conceal mode |

| 30 | Set foreground colour to Black |

| 31 | Set foreground colour to Red |

| 32 | Set foreground colour to Green |

| 33 | Set foreground colour to Yellow |

| 34 | Set foreground colour to Blue |

| 35 | Set foreground colour to Magenta |

| 36 | Set foreground colour to Cyan |

| 37 | Set foreground colour to White |

| 40 | Set background colour to Black |

| 41 | Set background colour to Red |

| 42 | Set background colour to Green |

| 43 | Set background colour to Yellow |

| 44 | Set background colour to Blue |

| 45 | Set background colour to Magenta |

| 46 | Set background colour to Cyan |

| 47 | Set background colour to White |

The Neotron application library allows access to the console via two means:

- Implicitly, through the use of the

println!macro. - Explicitly, through the use of the Standard Output file handle, obtained with

neotron::io::stdout()or by opening theCON$:device for writing.

The Neotron OS doesn't have a concept of 'Standard Error' as distinct from 'Standard Output'. Application libraries may wish to emulate this feature by, for example, printing any text output by eprintln! in a different colour.

Reading from CON$:

Performing a read on the console device will block the application until either the Enter key is pressed on the keyboard, or Control + C is pressed on the keyboard. If the Enter key is pressed, the UTF-8 encoding of the characters entered by the user are copied to the given buffer (up to as many as will fit). If too many characters are entered to fit in to the given buffer, the Console will beep and the user must use Backspace to remove some characters and free up some buffer space. Characters being entered are echoed to the console (although Conceal mode will help if the user is entering a password).

In the background during this function, the OS is polling the keyboard for key events, handling special keys (like Backspace, or Shift) and when a valid key is pressed, the matching Unicode character is UTF-8 encoded and added to the buffer.

On some Neotron systems, pressing the 'Up' arrow key will restore the previous command line contents (like when using the readline library on GNU/UNIX systems).

#![allow(unused)] fn main() { use neotron::fs::File; let mut buffer = [0u8; 16]; /// The standard Neotron file read functions can be used to read from the console. let mut console = File::open("CON$:") .expect("Failed to open console for reading"); match console.read(&mut buffer) { Ok(0) => { println!("You entered an empty string"); } Ok(n) => { // The Neotron OS guarantees this will be valid UTF-8 let read_string = unsafe { core::str::from_utf8_unchecked(&buffer[0..n]) }; println!("You entered {:?}", read_string); } Err(e) => { eprintln!("Oh, I got read error {:?} reading from the console", e); } } /// There is also a Neotron Application Library helper function which reads to a buffer (unlike the normal Rust Standard Library function which reads to a `String`). let bytes_read = neotron::io::stdin() .read_line(&mut buffer) .expect("Failed to read from console"); }

Reading from KBD$:

For some applications, such as games, the application will need raw key up/down events rather than the Unicode characters those key events correspond to. For this, there is a device which returns raw key events. Reading from this device is non-blocking. Mapping is performed if the current keyboard layout is non-QWERTY (e.g. the top left letter key on an AZERTY keyboard is Key::LetterA not Key::LetterQ), but you must perform your own handling of shifted characters (for example how Shift + . gives you a > character when using a United Kingdom keyboard layout). The easiest way to handle this is to allow users to map their own keys (e.g. "Press the key you want to use for 'Jump': ").

#![allow(unused)] fn main() { enum Key { LetterA, LetterB, LetterC, LetterD, ... Digit0, Digit1, ... Dot, Comma, PrintScreen, Up, Down, Left, Right, Home, End, Delete, ... } struct KeyEvent(u8); impl KeyEvent { unsafe fn from_octet(u8) -> KeyEvent; fn is_keydown(&self) -> bool; fn is_keyup(&self) -> bool; fn get_key(&self) -> Key; } use neotron::fs::File; let mut kb = File::open("KBD$:").expect("Failed to open raw keyboard"); let buffer = [0u8; 16]; /// The standard file read function is used to read from the keyboard match kb.read(&mut buffer) { Ok(0) => { println!("No raw key events available"); } Ok(n) => { for octet in buffer[0..n].iter() { let ev = unsafe { KeyEvent::from_octet(octet) }; println!("Received event {:?}", ev); } } Err(e) => { eprintln!("Oh, I got read error {:?} reading from the keyboard", e); } } }

Writing to KBD$:

The least significant (1) bit of any byte written to KBD$ sets the Num Lock light. The next (2) bit of any byte written to KBD$ sets the Caps Lock light. The next (4) bit of any byte sets the Scroll Lock light. This is useful if you are using raw keyboard mode to handle key events and want to perform your own Num Lock, Caps Lock and Scroll Lock handling.

Writing to TIME$:

Write an ASCII string in ISO-8601 format (e.g. 2020-01-01T15:44:21.031Z) to set the time.

Reading from TIME$:

Reading from this device will return an ASCII/UTF-8 string in ISO-8601 format (e.g. 2020-01-01T15:44:21.031Z).

# Reading the time in the Neotron Shell with the cat command

$ cat TIME$:

2020-01-01T15:44:21.031Z

$

Writing to GFX$:

Opening the GFX$mode=X: device puts the system into specified video mode X and gives access to the underlying video RAM. Optional x, y, width and height parameters allow a window to be created into video RAM, which is useful if you want to update a small region. Setting pixels on the screen is simply a case of seeking to the correct position and writing out as many bytes as required. The specific format of the bytes written to this device will depend on the current video mode. There is some other (TBD) mechanism obtain the list of supported video modes and their formats, but they will include Chunky modes (where multiple consecutive bits/bytes map to Red, Green and Blue components for each pixel) and Planar modes (where Red, Green and Blue each have their own distinct regions). This device is useful to blitting bitmaps to the screen, but drawing lines and circles is more efficiently performed through other OS APIs.

# Using the copy command in the Neotron Shell to put a picture at the top of the screen in Mode 7

$ copy 0:/EXAMPLE.GFX GFX$mode=7;height=150:

30000 bytes copied

$

Reading from GFX$:

Reading from this device allows an application to determine what is currently on the screen. The data is in the same format as when writing to the device.

Writing to PRNx$:

Ordinarily, every byte written to this device is sent to the Parallel Port, followed by high pulse on the STROBE pin and a busy-wait for the BUSY pin to return low. If any error signals are activated by the printer, the write is ended early.

Opening this device with the option raw, enables raw mode. In this mode, each write must be a two byte value:

- Byte 0 is 0x00 to write to the data pins or 0x01 to write to the control pins

- Byte 1 is the value to write to all eight data pins, or to the control pins as per the following table.

| Bit Number | Description |

|---|---|

| 0 | 1 to enable STROBE (active high) |

| 1 | 1 to enable LINE_FEED (active low) |

| 2 | 1 to enable RESET (active high) |

| 3 | 1 to enable SELECT_PRINTER (active low) |

In raw mode you can use the Parallel Port as a generic GPIO port with 12 output pins, and 5 input pins.

Reading from PRNx$:

A read will return one byte which is a bitmask of the status bits, regardless of whether it was opened in raw mode or normal mode.

| Bit Number | Description |

|---|---|

| 0 | 1 when ERROR is active (low) |

| 1 | 1 when SELECT_IN is active (high) |

| 2 | 1 when PAPER_OUT is active (high) |

| 3 | 1 when ACK is active (low) |

| 4 | 1 when BUSY is active (low) |

Writing to DISCx$:

Allows access to the raw blocks on a disk. Useful for writing out disk images. Support for creating partition tables is TBD, and may have to be done at the application level by writing to the first sector on disk. Writing to raw disk structures whilst files are open on that volume is likely to lead to filesystem corruption.

Reading from DISCx$:

Allows access to the raw blocks on a disk. Useful for taking disk images, or inspecting raw disk structures. The option partition=X allows a specific partition to be selected, where 1 to 4 are the first four Primary partitions, and 5 or greater selects a Logical Partition located within the Extended Partition. Inspecting the partition metadata (start, end, filesystem type, etc) must be done at the application level by reading the first sector.

Opening 'SERx$:'

| Option | Description |

|---|---|

| handshaking=rtscts | Enable RTS/CTS handshaking |

| handshaking=xonoff | Enable XON/XOFF handshaking |

| handshaking=none | Disable handshaking (default) |

| bps=X | Set bitrate to X bits per second |

| timeout=X | Set read/write timeout to X frames |

| timeout=none | Block forever on read/write |

| timeout=0 | Never block on read/write |

Writing to SERx$:

A write will block until all of the octets have been transmitted to the remote device at the specified bit rate, or a timeout occurs (if specified).

Reading from SERx$:

A read will block until the given number of octets have been received from the remote device at the specified bit rate, or a timeout occurs (if specified).

Opening 'TONEx$:'

No options when opening TONE devices.

Writing to TONEx$:

A tone is specified with three parameters:

- A frequency, in Hertz.

- A waveform (e.g. Square, Sine, Triangle, White Noise, etc)

- A volume (between 1 and 16)

These three parameters are packed into four bytes:

Byte 0 Byte 1 Byte 2 Byte 3

+-------------+-------------+-------------+-------------+

|Frequency LSB|Frequency MSB|Waveform |Volume |

+-------------+-------------+-------------+-------------+

The buffer written must be a multiple of four octets in length.

Reading from TONEx$:

Not supported.

Opening 'PCMx$:'

| Option | Description |

|---|---|

| channels=N | Enable N channels (default is 1) |

| bits=U8 | Set 8-bit linear unsigned samples |

| bits=S8 | Set 8-bit linear signed samples |

| bits=U16 | Set 16-bit linear unsigned samples |

| bits=S16 | Set 16-bit linear signed samples |

| rate=X | Configure for X samples per second |

Writing to PCMx$:

When the PCM device is opened, the number of channels (mono/stereo), sample rate (e.g. 22,050 Hz), bit depth (e.g. 8 bits) are specified. The bytes written are the samples to be played, as little-endian integers. If there are multiple channels, the samples for each channel are supplied in turn before moving on to the next sample (e.g. Left Sample N, Right Sample N, Left Sample N+1, Right Sample N+1). You should write sufficiently often to avoid underflowing the internal PCM buffer.

Reading from PCMx$:

When the PCM device is opened, the number of channels (mono/stereo), sample rate (e.g. 22,050 Hz), bit depth (e.g. 8 bits) are specified. The bytes read are the samples which have been recorded, as little-endian integers. If there are multiple channels, the samples for each channel are supplied in turn before moving on to the next sample (e.g. Left Sample N, Right Sample N, Left Sample N+1, Right Sample N+1). You should read sufficiently often to avoid overflowing the internal PCM buffer.

Writing to JSx$:

Not supported

Reading from JSx$:

Returns a bitmask of inputs from that joystick:

| Bit Number | Description |

|---|---|

| 0 | Up |

| 1 | Down |

| 2 | Left |

| 3 | Right |

| 4 | Fire 1 (B) |

| 5 | Fire 2 (C) |

| 6 | Fire 3 (A) |

| 7 | Fire 4 (Start) |

Yes, the fire buttons are in that order - mainly because on a Master System pad, you only have Fire Button 1 and Fire Button 2, but on a Mega Drive pad, those same pins on the interface correspond to Fire Buttons B and C. If you have a standard Atari/Commodore joystick, you will probably only have Fire Button 1.

The OS will poll the joystick once per video frame, so attempting to read more often than that will given repeated results. A fire button is very likely to be held for multiple frames, so you will need to store the previous reading and check which bits have flipped since last time.

Threads and Processes

The Neotron OS has no support for running multiple processes, nor for multi-threading, nor for multi-core systems. It is very much like MS-DOS and CP/M in this regard. It does, however, use locks to ensure that should the use of interrupts cause a function to be 're-entered', the situation is caught gracefully rather than leading to system instability. A user is, therefore, free to implement multi-threading within their application if they so wish.

Memory Allocation

The Neotron BIOS initialise all of the RAM, configures a stack, reserves a further portion of RAM for its own use, and passes the OS a structure which describes the start and end address of each contiguous block of remaining memory (and there may be several if your CPU has multiple separate SRAMs). From this remainder, the Neotron OS allocates what it needs for its own purposes.

The Neotron OS has a built-in heap memory allocation routine (like malloc) and matching deallocation routine (like free) and it offers these to the currently running application. This saves the application having to include its own memory allocation routines. When an application is loaded, the heap is automatically set to use all of the remaining un-used RAM (which varies depending on the size of the application). Applications are usually (but not always) given the same stack as the OS and the BIOS, and so it is very possible for a badly behaved application to corrupt and/or crash the entire system.

An application can always assume its own RAM for code and global variables starts at address 0x2000_0000. The memory allocation routines may return an address from some other range (e.g. the AXI SRAM on an STM32H7 is at 0x2400_0000).

Networking

The TCP/IP stack offers a Berkley Sockets style API. Supported devices will include an SPI based Ethernet MAC/PHY devices (such as the Microchip ENC28J60) using smoltcp, and UART based Ethernet/WiFi/Cellular devices with on-board TCP/IP stack (such as the ESP-01).

The Neotron OS - API Calls

The OS exports its functionality to each Application through a structure of function pointers. This structure exists in OS memory (probably in Flash, but it could be in RAM) and a pointer to it is passed to the Application when it is started by the OS. This is the same process as used when the BIOS starts the OS.

The Application should only access the hardware and the operating system state through the function pointers contained within the given structure. The only assumption the Application can make is about the location of the memory regions defined in its Linker Script.

The OS API is (or will be) documented at https://github.com/Neotron-Compute/Neotron-API.

The Neotron Command Shell

Introduction

The Neotron Shell is the first application started by the OS. It allows the user to give the system commands, including:

- Browsing filesystems on the SD card

- Loading files from SD card into RAM

- Inspecting the contents of RAM and ROM

- Executing applications

The Shell uses the standard OS API and hence is much like a normal application. The only difference is that it uses a special region of memory, allowing it to remaining running whilst it loads another application into the main program area. Once that application is started, it can use the shell's memory region as it's own - the OS will re-initialise the shell when the application exits.

Analogies from the PC world would include MS-DOS's COMMAND.COM and CP/M's CCP, but at a functional level it's more like the U-Boot Shell.

Shell Expansion

Any argument of the form ${VAR} is replaced with the value stored in the environment variable called VAR.

Any argument containing a * character is taken to be a glob and is expanded to all the filenames matching that glob. Note that there are a limited number of arguments that can be given to a command, so attempts to glob more files than that number will generate an error.

Magic Devices

The OS supports a number of magic device filenames. The shell is unaware of this and just asks the OS to perform the specified operation on the given filenames.

Shell Commands

DIR [/S] [<path>]

Performs a directory listing, either for the current drive and directory or of the given absolute or relative path.

The /S option displays directories recursively.

MKDIR [/P] <path>

Creates a new directory, given either an absolute path or a relative path. Can optionally make all the intermediate paths too.

TYPE <path>

Displays the contents of a file, assuming it is ASCII text.

HEXDUMP <path>

Displays the contents of a file as hex encoded binary.

COPY [/S] <source1> [<source2>...] <dest>

Copies one or more files from one location to another. If one sourceX is

specified dest can be a file or a directory. If multiple sourceX files are

specified, dest must be a directory. The argument /S makes COPY look in

subdirectories recursively.

RENAME <old> <new>

Changes the name of a file. Cannot move files between directories or drives.

MOVE <src> <dest>

Moves a file from one directory to another. The dest path can be on a

different drive or in a different directory.

DEL <path> [<path2>...]

Deletes one or more files.

RMDIR <path> [<path2>...]

Deletes one or more empty directories.

DELTREE <path> [<path2>...]

Recursively deletes one or more directories.

PEEK <addr>

Displays the contents of ROM or RAM at the given address.

POKE <addr> <value>

Writes a new value to RAM at the given address. Attempts to write to ROM are ignored.

SAVE <addr> <length> <file>

Copies RAM or ROM to a file on disk.

LOAD <path>

Copies the contents of a file on disk to RAM.

EXEC <path>

Performs a LOAD of the given file, followed by a RUN. This command is implied if a command is given which matches the name of a file in the current directory, or in the system's PATH environment variable.

RUN

Runs a program already in memory (e.g. having used LOAD)

SET <var> <value>

Sets an environment variable to the given value. The value var should not include ${ or }.

$ SET PATH 0:/BIN;0:/OS/BIN

ECHO <text>

Prints some text to the console.

$ ECHO "Hello, world"

LOADENV <path>

Loads environment variables from a file.

$ LOADENV ./FILE.ENV

SAVEENV <path>

Saves environment variables to a file.

$ SAVEENV ./FILE.ENV

SCRIPT <path>

Runs the shell commands found in the given filename.

$ SCRIPT ./FILE.CMD

EDIT <path>

Starts a full-screen text editor.

$ EDIT 1:/README.TXT

DEV

Shows the list of devices reported by the BIOS.

VOL

Shows the current list of volumes, by drive. Includes their volume names, format and storage capacity.

SCAN

Re-scans the given device for volumes. Volumes which are no longer present (e.g. because the disk has been removed) are de-allocated their volume ID. New volumes are allocated new volume IDs.

CD [<dir>]

Change the current directory. May include a volume ID, or be relative to the current volume, or the current directory. Unlike MS-DOS, there is only one current directory for the whole system (instead of one for each drive).

ATTR [/A] [/A-] [/H] [/H-] [/R] [/R-] [/S] [/S-] <path>

Gets or sets a file's attributes (Archive, Hidden, Read Only, and System).

The /X flag sets a the relevant bit. The /X- flag unsets it.

$ # Set System, Hidden and Read Only, but clear Archive

$ ATTR /A- /S /H /R SYSTEM.DAT

The Neotron Menu Shell

In some cases, the Neotron Command Shell is a little too bare-bones. Perhaps the primary use of the Neotron is to play some games, or perhaps you want to browse the SD quickly using a GUI. For these situations, you can set your default shell to be the Menu Shell.

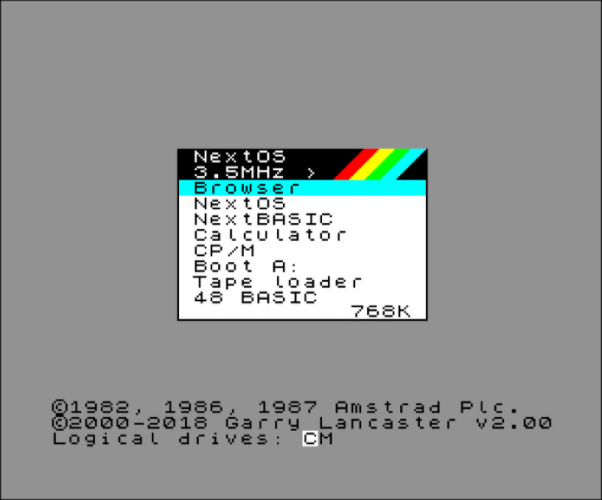

The Menu Shell is inspired by the boot-up menu on NextOS for the Spectrum Next.

The Neotron Menu is displayed in text-mode (nominally 48x36) and offers a series of options the user can scroll between using the arrow keys on a PS/2 keyboard or a Joystick in Port 1. These options all correspond to an item in the Neotron Command Shell, and so there is no extra functionality offered by the Neotron Menu Shell - it just makes existing functionality easier to access. Note that the final item on the list exits the Neotron Menu Shell and replaces it as the current shell with the Neotron Command Shell.

- File Manager - allows the user to browse the list of volumes, and the files and directories on those volumes. It supports the usual Create/Move/Rename/Copy/Load/Delete operations.

- Tiny BASIC - loads Tiny BASIC compiled as Neotron Application.

- 6502 BASIC - loads a 6502 Emulator, which then runs Enhanced BASIC.

- Test Video - runs through the various graphical/text video modes.

- Test Audio - runs through the various tones that can be generated.

- Test Parallel Port - displays the printer status, and optionally sends some ASCII text to the parallel printer port.

- Configure Date/Time - displays the current RTC status and allows the date/time to be set.

- Configure Keyboard - allows the keyboard to be tested, and the layout selected

- MIDI Keyboard - allows you to use the Neotron as a synthesiser, by connecting a MIDI Keyboard to the MIDI In port.

- Configure WiFi - allows you to browse the WiFi networks, and join a particular network.

- Serial Terminal - allows you to exchange characters with any serial port in the system, including the RS-232 port and the WiFi interface.

Neotron Applications

Neotron Applications are loaded into RAM and then executed. For portability, they should use the API provided by the OS, but the system implements no security features or memory-protection, so once they are running, they have complete control of the entire system.

Existing applications include:

- A text-mode Snake game

- A 6502 emulator which runs 6502 Enhanced BASIC

- Tiny BASIC

- A slideshow/presentation tool

- A simple synthesiser which plays notes according to MIDI input

Neotron Hardware

The Netron OS is intended to be binary-portable across any machine with a Neotron BIOS. How that works out in practice remains to be seen, but that's the goal. As the BIOS API, example BIOS implementations and the OS itself are entirely open, anyone can build their own Neotron-compatible system, using any ARMv7-M compatible processor. However, there will naturally be value in having some commonality between Neotron systems, in order to reduce development effort.

Another important factor in the Neotron Hardware is that, like the software, it should be fully Open. That is, anyone should be able to pick up a Neotron System and understand it right down to the component parts (and why those component parts were chosen). It isn't sufficient to simply post some Gerbers on GitHub and call it done - any more than it would be to post some compiled firwmware binaries. Making an Open System means making a system where people are invited and encouraged to learn everything there is to know about that system.

Components

A Neotron System will naturally be comprised of:

- A microcontroller, also known as a System On Chip (SoC) - this will contain one or more Processor Cores, RAM, possibly Flash, and some internal peripherals

- The processor core will be compatible with the ARMv6-M ISA*.

- External peripherals - such as UART level shifters, audio amplifiers, SD cards

- A baseboard (tradtionally known as a motherboard) - a PCB which holds the SoC, the external peripherals, and any connectors

* The ARMv6-M ISA (as implemented by the Cortex-M0/M0+ processore cores) has fewer instructions, and so is easier to understand. However, ARMv6-M has no Compare-and-Swap Atomic instructions, meaning that sharing data between the main thread and interrupts can be more complicated in some situations. It is TBD as to whether this is too much of a burden for the OS to carry and we may need to raise the minimum to ARMv7-M ISA, i.e. a Cortex-M3 or higher.

The System On Chip

Picking a SoC

When it comes to picking an SoC for a new Neotron model, the following are important criteria:

Mandatory (MUST):

- Use an ARMv6-M compatible core (i.e. any Arm Cortex-M)

- Generate digital RGB video at 25.175 MHz or 40 MHz, or some integer fraction thereof

- Anything between 1-bit and 24-bits per pixel is acceptable.

- VESA specify a 0.5% clock tolerance, so between 25.05 MHz and 25.3 MHz is OK

- 40 MHz gives you 800x600 (and hence 400x600, 200x600, etc)

- 25.175 MHz gives you 640x480 (and hence 320x480, 160x480, etc)

- If you aren't performance sensitive (i.e. playing games), you could have off-chip video support implemented on a second processor, with a fast communications link (e.g. Quad SPI) between them

- You can easily scan-double the output just by playing each line twice (or three times...)

- Have a four-wire UART, or an ARM Serial Wire Debug interface, for debug logging

- Have at least 256 KiB of memory for BIOS / OS code (in Flash or RAM)

- Have enough RAM to support the desired video modes (80x25 text mode is 4,000 bytes, while 800x600 @ 8bpp needs around 470 KiB)

- Have at least 64 KiB of free application RAM (ideally 256 KiB or more)

- Have an SPI Controller interface which can run at least 25 MHz

- Have 7 or more chip-select output pins

- If you are limited on pins, you can use a

74LS1383:8 decoder for the chip-selects

- If you are limited on pins, you can use a

- Have 8 interrupt input pins

- If you are limited on pins, you can use an

MCP23S17to mux 16 interrupts inputs down to 1

- If you are limited on pins, you can use an

- Have an I²C Controller interface which can run at 400 kHz

- Have either an I²S audio codec interface, or stereo PWM audio output pins

- Have a ROM bootloader which can boot from UART, USB or SD Card

- This is so home-made systems do not require an ARM debug probe for initial programming

- Have a footprint that is easy to professionally assemble on a simple 4-layer PCB without micro-vias, i.e. one of

- 0.8mm+ pitch ball grid array (BGA) package

- 0.5mm+ pitch quad flip-chip package (QFP), shrink small-outline package (SSOP) or small-outline IC (SOIC)

- Have 3.3V I/O

- Cost under $20 in one-off quantities

- Be available from mainstream catalog vendors (e.g. Digikey)

Desirable (SHOULD)

- Use an ARMv7-M compatible core (i.e. Arm Cortex-M3, Cortex-M4, Cortex-M7 or Cortex-M33)

- Have at least one USB 2.0 Host or OTG port (High-Speed or Full-Speed)

- Has a footprint that is easy (or at least possible) to hand-assemble at home:

- 0.8mm pitch QFP (e.g. 7x7mm QFP32)

- 1.27mm pitch SOIC

- Takes a 3.3V power input which is internally regulated down to the desired core voltage

- Where multiple rails are required, we either need relaxed requirements in sequencing, or an available PMIC chip which brings the rails up in the right order

- Be available from the JLCPCB Parts Catalog

- Supports additional external RAM (either SRAM, SDRAM or QSPI HyperRAM)

We've identified the following parts as meeting some or more of the above criteria:

| Manuf. | Part Number | Core | Clock (MHz) | Package | RAM (K) | Flash (K) | Price (10 off) | Notes |

|---|---|---|---|---|---|---|---|---|

| ST | STM32L552ZET6 | Cortex-M33 | 110 | LQFP 144 | 256 | 512 | £6.65 | Supports HyperRAM, and TrustZone, and is low-cost |

| ST | STM32H730ZBT6 | Cortex-M7 | 550 | LQFP 144 | 564 | 128 | £6.97 | Great value due to small Flash. SPI SRAM support. |

| ST | STM32H7A3ZIT6 | Cortex-M7 | 280 | LQFP 144 | 1344 | 2048 | £11.00 | Big SRAM - might not need external RAM? |

| ST | STM32H743ZGT6 | Cortex-M7 | 480 | LQFP 144 | 1024 | 1024 | £13.75 | Cheapest H7 with 1 MiB SARM. No SPI SRAM support - will require SDRAM |

| TI | TM4C1299KCZADI3 | Cortex-M4 | 120 | VFBGA 212 | 256 | 512 | £11.78 | Poor value, but same family as Neotron-32 |

| NXP | IMXRT1062DVJ6A | Cortex-M7 | 600 | BGA 196 | 1024 | External | £10.41 | As used on Teensy 4.1. HyperRAM support. |

| Raspberry Pi | RP2040 | 2x Cortex-M0+ | 133 MHz | QFN 56 | 256 | External | £0.85 | Incredibly cheap. Cortex-M0 only supports ARMv6-M. No RAM upgrades |

It is worth also considering the Lattice range of small, low-cost FPGAs, and loading an RISC-V soft-core like the VexRiscv.

Video from a System On Chip

Video support from your SoC can vary greatly - from SoCs which basically have no video support but can be 'tricked' into generating a signal that's sort-of VGA compatible, to SoCs which have on-board graphics accelerators that can render multiple semi-transparent planes together.

Video Modes

First, we should discuss the concept of a video mode. This is a collection of parameters which describe the picture that is being generated.

Timing

In this section, we generally assume that the video is VGA-like - that is, each frame is drawn line-by-line, starting with the top line and moving downwards. A line comprises pixels, which are drawn from left to right. Each pixel has a colour, which can be anywhere between 'on or off' or 'one of 16.8 million colours'. As the pixels are drawn left to right, there will be some extra non-visible 'off-screen' pixels, which are designed to give an old-fashioned cathode-ray tube (CRT) monitor time to move the scanning 'gun' back over to the left hand side of the image ready to draw the next line. In the same fashion, there will be some non-visible 'off-screen' lines which give a CRT's gun time to move back to the top of the frame. Although we almost universally use LCD monitors now, the standards still include these 'blanking periods'.

The monitor is able to find the visible picture within the signal, thanks to the provision of two extra signals - Horizontal Sync and Vertical Sync. These pulse high (or low) during the middle of the relevant blanking period.

The relevant parameters are:

- Horizontal Visible Pixels - the number of visible pixels on each line

- Horizontal Front Porch - the number of non-visible pixels before the sync pulse

- Horizontal Sync Width - the number of non-visible pixels during the sync pulse

- Horizontal Back Porch - the number of non-visible pixels after the sync pulse

- Horizontal Pixels - the total number of pixels on each line

- Horizontal Scan Rate - the number of lines (visible or non-visible) drawn per second

- Vertical Visible Lines - the number of visible lines in each frame

- Vertical Front Porch - the number of non-visible lines before the sync pulse

- Vertical Sync Width - the number of non-visible lines during the sync pulse

- Vertical Back Porch - the number of non-visible lines after the sync pulse

- Vertical Lines - the total number of lines in each frame

- Frame Rate (or Refresh Rate, or Vertical Scan Rate) - the number of complete frames drawn per second

- Pixel Clock (or Dot Clock) - the number of pixels (visible or non-visible - we'll get to that shortly) produced per second

These terms are related as follows:

Horizontal Pixels = Horizontal Visible Pixels + Horizontal Front Porch + Horizontal Sync Width

+ Horizontal Back Porch

Vertical Lines = Vertical Visible Lines + Vertical Front Porch + Vertical Sync Width

+ Vertical Back Porch

Horizontal Scan Rate = Pixel Clock / Horizontal Pixels

Frame Rate = Horizontal Scan Rate / Vertical Lines

Your monitor will place limits on the values for Frame Rate, Horizontal Scan Rate and Vertical Lines. An analog CRT generally doesn't care about Horizontal Pixels and Pixel Clock - provided the Horizontal Scan Rate is within range - although if you push this beyond the maximum bandwidth of you display (or your cable) the signal starts to get 'smoothed' and the greater definition is lost. A digital display, like an LCD monitor, will sample the analog horizontal signal at fixed intervals and if your source doesn't match perfectly, you may get a fuzzy picture. Generally, the number of horizontal pixels your monitor is looking for is a function of the number of vertical lines, calculated from some look-up table of common video standards.

Colours

The monitor generally doesn't care about the number of colours each pixel can take, as the pixels are transmitted as analog red, green and blue signals (0.7V peak). However, the SoC will care as the pixels must be stored digital and the more bits per pixel, the more bytes of framebuffer RAM we require!

Standards

The original IBM standard for the Video Graphics Array included the following video modes:

| H. Vis | V. Vis | H. Tot | V. Tot | H. Freq | Frame Rate | Pixel Clock | Used for |

|---|---|---|---|---|---|---|---|

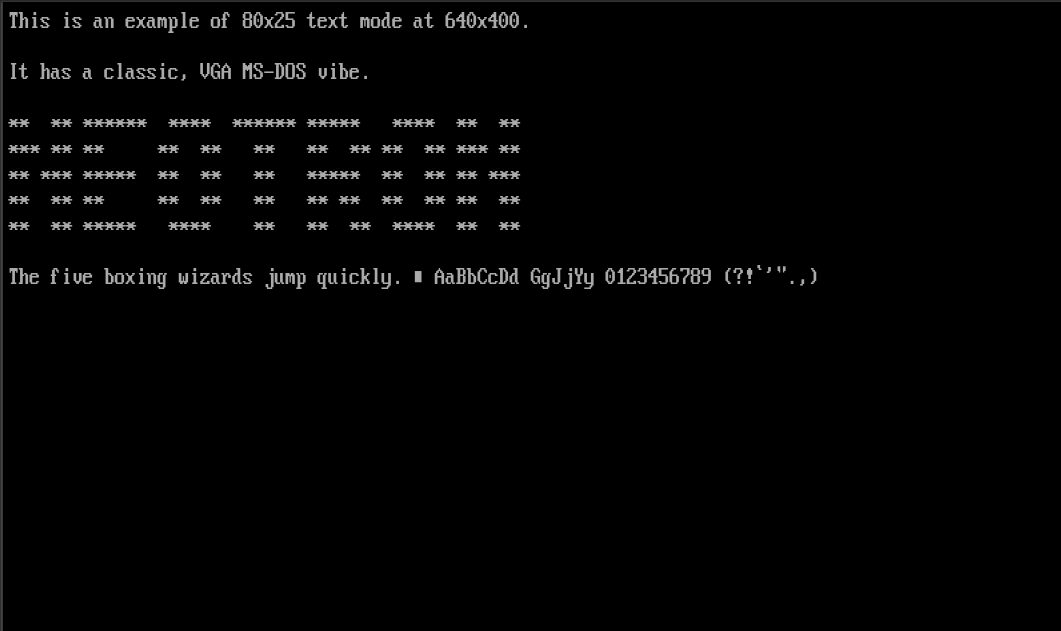

| 720 | 400 | 900 | 449 | 31.469 kHz | 70 Hz | 28.322 MHz | Default 80x25 Text mode |

| 640 | 480 | 800 | 525 | 31.469 kHz | 60 Hz | 25.175 MHz | High-res graphics mode |

| 640 | 400 | 800 | 449 | 31.469 kHz | 70 Hz | 25.175 MHz | 80x25 text with mixed graphics |

| 720 | 350 | 900 | 449 | 31.469 kHz | 70 Hz | 28.322 MHz | MDA compatible text mode (720x400 with extra blanking) |

| 640 | 350 | 800 | 449 | 31.469 kHz | 70 Hz | 25.175 MHz | EGA compatible text/graphics (640x400 with extra blanking) |

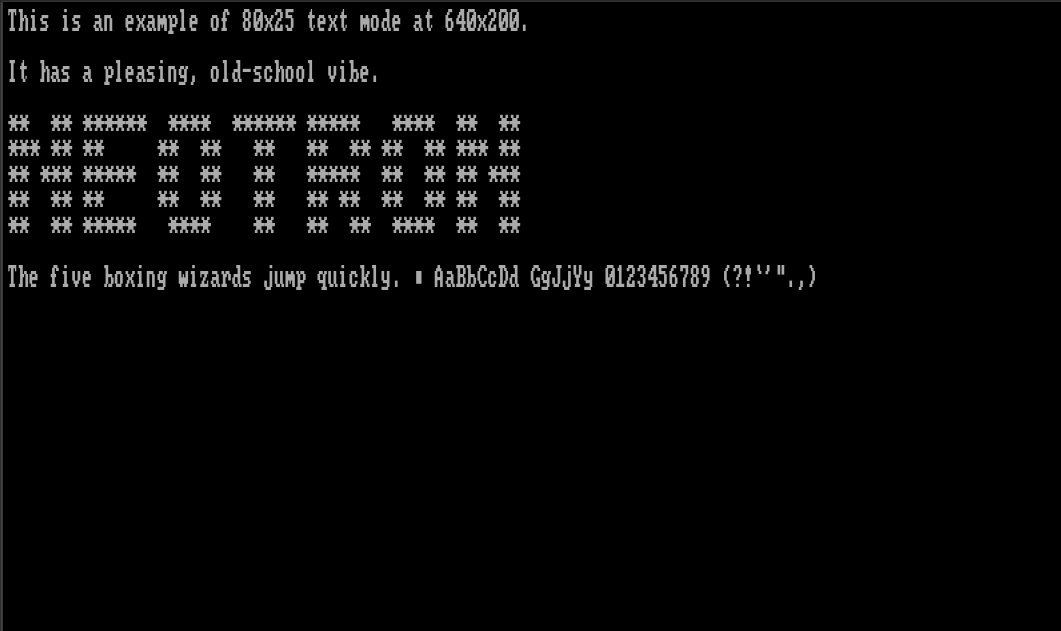

| 640 | 200 (2x) | 800 | 449 | 31.469 kHz | 70 Hz | 25.175 MHz | CGA compatible text/graphics mode |

| 320 | 240 (2x) | 400 | 525 | 31.469 kHz | 60 Hz | 25.175 MHz | Low-res, high-colour mode |

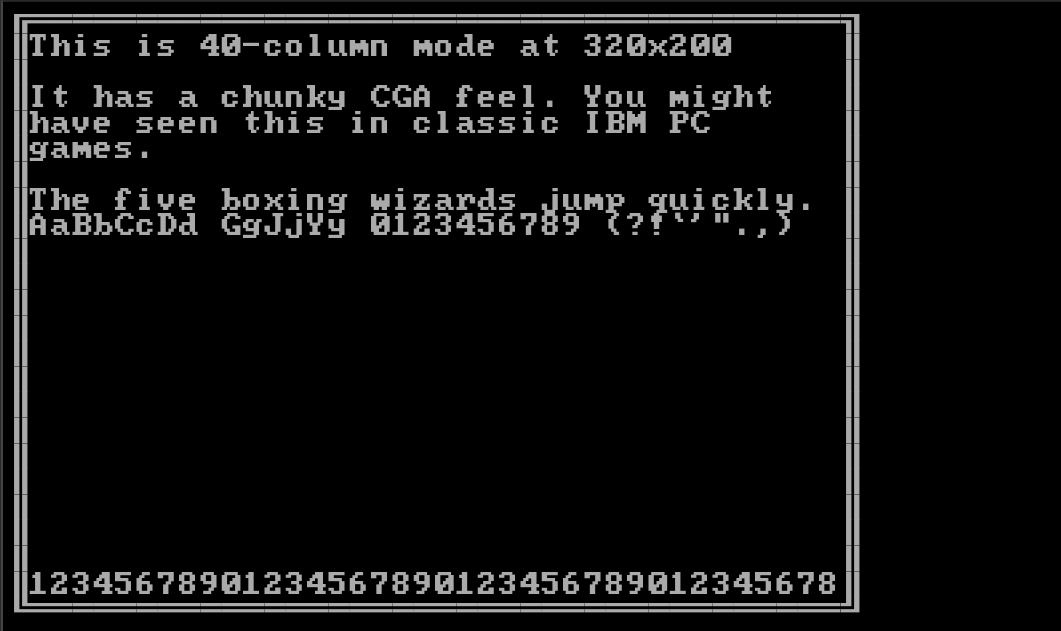

| 320 | 200 (2x) | 400 | 449 | 31.469 kHz | 70 Hz | 25.175 MHz | CGA compatible text/graphics graphics mode |

We see from this table that there are only two values for the Vertical Total Lines - 525 for 480-line modes and 449 for 350/400-line modes - corresponding to frame rates of 60 Hz and 70 Hz respectively. There is also the option to increase the pixel clock up from 25.175 MHz to 28.322 MHz, increasing the number of pixels per line from 800 to 900. This, in turn, increases the number of pixels per character on an 80-column text mode display from 8 to 9. Finally, we can simply halve the pixel clock to lower the horizontal resolution, which saves video memory and allows for more colours on screen.

The rates marked (2x) simply have each line drawn twice by the VGA card, in order to keep the Horizontal Frequency at the standard value.

During the 1990s, the resolutions and colour depths supported by video cards increased greatly, and monitors began to support a wider range of horizontal frequencies. These various modes were standardised by the Video Electronics Standards Association (VESA), and there are too many to list here. However, some modes of note include:

| H. Visible | V. Visible | H. Total | V. Total | H. Freq | Frame Rate | Pixel Clock |

|---|---|---|---|---|---|---|

| 800 | 600 | 1056 | 628 | 37.9 kHz | 60 Hz | 40.0 MHz |

| 1024 | 768 | 1344 | 806 | 48.4 kHz | 60 Hz | 65.0 MHz |

| 1280 | 720 | 1664 | 748 | 44.8 kHz | 60 Hz | 74.5 MHz |

| 1920 | 1080 | 2576 | 1120 | 67.2 kHz | 60 Hz | 173.000 MHz |